## **SSC8814CS6A**

## **Dual N-channel Power MOSFET**

### Features

| ١ | / <sub>DS</sub> | V <sub>GS</sub> | R <sub>sson</sub> Typ. | ID | ESD  |

|---|-----------------|-----------------|------------------------|----|------|

| 1 | 2V              | ±8V             | 10mR/4.5V              | 8  | 800V |

## Description

The SSC8814CS6A is the Dual N-Channel enhancement MOSFET. Uses advanced trench and CSP package technology design to provide excellent R<sub>ON</sub> with low gate charge.

## Application

- Power Switch

- Load Switch

- One-cell Lion Battery

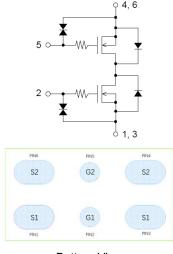

# Pin Configuration

**Bottom View**

## Ordering Information

| Device      | Package | Shipping |  |  |

|-------------|---------|----------|--|--|

| SSC8814CS6A | CSP     | 3K/Reel  |  |  |

# ♣ Absolute Maximum Ratings(TA=25°C unless otherwise noted)

| Symbol           | Parameter                                           | Ratings | Unit |  |

|------------------|-----------------------------------------------------|---------|------|--|

| V <sub>SS</sub>  | Source -to-Source Voltage                           | 12      | V    |  |

| V <sub>GS</sub>  | Gate-to-Source Voltage                              | ±8      |      |  |

| I <sub>D</sub>   | Continuous Source Current <sup>A</sup> 8            |         | ^    |  |

| I <sub>DM</sub>  | Pulsed Source Current <sup>B</sup>                  | 24      | Α    |  |

| P <sub>D</sub>   | Power Dissipation <sup>C</sup>                      | 1       | W    |  |

| TJ               | Operation junction temperature 15                   |         | °C   |  |

| T <sub>STG</sub> | Storage temperature range                           | -55~150 |      |  |

| $R_{\theta JA}$  | Junction-to-Ambient Thermal Resistance <sup>c</sup> | 125     | °C/W |  |

# **↓** Electronics Characteristics(TA=25°C unless otherwise noted)

| Symbol                   | Parameter                         | Test Conditions       | Min | Тур. | Max | Unit |

|--------------------------|-----------------------------------|-----------------------|-----|------|-----|------|

| V <sub>(BR)SSS</sub>     | Source to Source                  | VGS=0V , IS=1mA       | 12  |      |     | V    |

|                          | Breakdown Voltage                 |                       |     |      |     | V    |

| $V_{\text{GS(TH)}}$      | Gate Threshold Voltage            | VSS=6V , IS=1mA       | 0.4 | 0.7  | 1.2 | V    |

| D                        | Source to Source on               | VGS=4.5V , IS=4A      |     | 10   | 14  | mR   |

| R <sub>SS</sub>          | Resistance                        | VGS=2.5V , IS=2A      |     | 15   | 22  |      |

| I <sub>SSS</sub>         | Zero Gate Voltage                 | VSS=10V , VGS=0V      |     |      | 1 u | uA   |

|                          | Current                           | V33-10V , VG3-0V      |     |      | ı   | uA   |

| $I_{GSS}$                | Gate Source Leak                  | VGS=±8V , VSS=0V      |     |      | ±10 | uA   |

| IGSS                     | Current                           | VGG-10V , VGG-0V      |     |      | 110 | u/\  |

| Vss                      | Forward Voltage                   | ISS=2A                |     | 0.7  | 1.3 | V    |

| C <sub>ISS</sub>         | Input Capacitance <sup>D</sup>    | VGS=0V                |     | 2700 |     |      |

| Coss                     | Output Capacitance <sup>D</sup>   | VSS=10V               |     | 450  |     | pF   |

| $C_{RSS}$                | Transfer Capacitance <sup>D</sup> | f=1MHz                |     | 290  |     |      |

| $T_{D(ON)}$              | Turn-on delay time                | VSS=6V                |     | 4    |     |      |

| T <sub>R</sub>           | Rise time                         | VSS-6V<br>IS=2A       |     | 5    |     | us   |

| T <sub>D(OFF)</sub>      | Turn-off delay time               | VGS=4V                |     | 13   |     | us   |

| T <sub>F</sub> Fall time |                                   | V 00-7 V              |     | 8    |     |      |

| $Q_{G}$                  | Total Gate Charge <sup>D</sup>    | VSS=6V, IS=2A, VGS=4V |     | 26   |     | nC   |

#### Note:

- A. The current rating is based on the  $t \le 10s$  thermal resistance rating.

- B. t=10us, Duty Cycle≤1%.

- C. Surface mounted on ceramic substrate.

- D. Guaranteed by design, not subject to production testing.

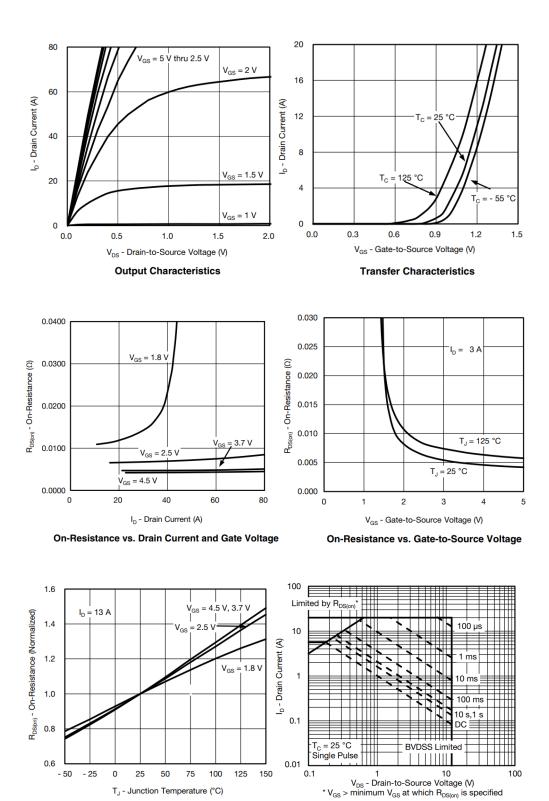

# ♣ Single Typical Characteristics(TA=25°C unless otherwise noted)

Safe Operating Area, Junction-to-Ambient

On-Resistance vs. Junction Temperature

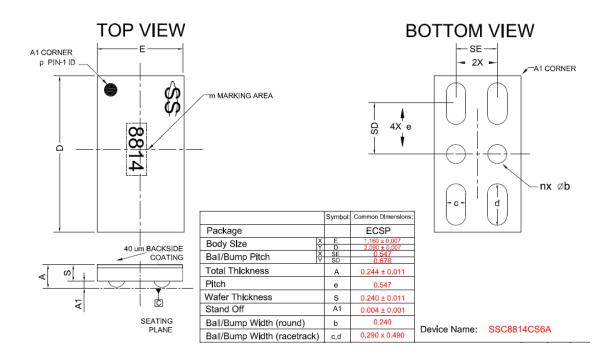

## Package Information

### **DISCLAIMER**

AFSEMI RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. AFSEMI DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICIENCE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

THE GRAPHS PROVIDED IN THIS DOCUMENT ARE STATISTICAL SUMMARIES BASED ON A LIMITED NUMBER OF SAMPLES AND ARE PROVIDED FOR INFORMATIONAL PURPOSE ONLY. THE PERFORMANCE CHARACTERISTICS LISTED IN THEM ARE NOT TESTED OR GUARANTEED. IN SOME GRAPHS, THE DATA PRESENTED MAY BE OUTSIDE THE SPECIFIED OPERATING RANGE AND THEREFORE OUTSIDE THE WARRANTED RANGE.